# Prehľad rodín FPGA a CPLD obvodov významných výrobcov

## Cieľ prednášky

Predstaviť riešenia FPGA a CPLD obvody najznámejších svetových výrobcov. Prehľad bude zameraný hlavne na najperspektívnejšie rodiny.

## Obsah

- Altera,

- Xillinx,

- Actel,

- Lattice

## Vývojové kity

- Altera (dostupné na KEMT)

# Altera (<u>www.altera.com</u>)

Existujúce rodiny

FPGAs

Stratix II

Stratix

Cyclone II

Cyclone

Stratix GX

APEX II

APEX 20K

Mercury

FLEX 10K

ACEX 1K

FLEX 6000

#### CPLDs

- MAX II

- MAX 3000A

- ▶ <u>MAX 7000</u>

#### **Structured ASICs**

- About HardCopy

- HardCopy II

- HardCopy Stratix

- HardCopy APEX 20K

## **Device Family Overview**

- <u>CPLDs</u>

- Low-Cost FPGAs

- High-Density FPGAs

- <u>Structured ASICs</u>

|      | Device | General Description                                         | Unique Features                                                                                                                                                                                                             |

|------|--------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLDS | MAX    | Lowest-cost, single-chip, easy-to-<br>use CPLD family       | <ul> <li>Lowest CPLD cost &amp; power consumption</li> <li>Highest CPLD density &amp; performance</li> <li>Instant-on, non-volatile</li> <li>User flash memory</li> <li>1.8-V, 2.5-V &amp; 3.3-V supply voltages</li> </ul> |

| ō    | MAX.   | Low-cost CPLD for lower-<br>complexity, low-density designs | <ul> <li>Low to moderate density</li> <li>Instant-on, non-volatile</li> <li>5-V I/O support</li> <li>Deterministic timing</li> <li>2.5-V, 3.3-V or 5.0-V<br/>supply voltages</li> </ul>                                     |

| Low-Cost FPGAs | Cyclone <sup>®</sup> II | Second-generation, lowest-cost<br>family in the Cyclone™ FPGA<br>series for designs where cost<br>concerns outweigh the need for<br>performance or extensive features | <ul> <li>Nios<sup>®</sup> II embedded<br/>processor support</li> <li>Embedded 18x18 digital<br/>signal processing<br/>(DSP) multipliers</li> <li>Moderate on-chip<br/>memory</li> <li>Moderate-speed I/O &amp;<br/>memory interfaces</li> <li>Broad intellectual<br/>property (IP) portfolio<br/>support</li> </ul> |

|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Cyclone 🖗               | First-generation, lower-density,<br>low-cost family in the Cyclone<br>FPGA series                                                                                     | <ul> <li>Nios II embedded<br/>processor support</li> <li>Low to moderate on-chip<br/>memory</li> <li>Low to moderate-speed<br/>I/O &amp; memory interfaces</li> <li>Broad IP portfolio<br/>support</li> </ul>                                                                                                       |

|                |                         |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                     |

| Density FPGAs  | Stratix 11              | General-purpose FPGA family<br>with the largest density & fastest<br>performance                                                                                      | <ul> <li>Nios II embedded<br/>processor support</li> <li>The most DSP blocks</li> <li>Large on-chip memory</li> <li>High-speed I/O &amp;<br/>memory interfaces</li> <li>1-Gbps dynamic phase<br/>alignment (DPA) with<br/>source-synchronous<br/>signaling</li> <li>Broad IP portfolio<br/>support</li> </ul>       |

| High-De        | Stratix                 | General-purpose, high-<br>performance FPGA family                                                                                                                     | <ul> <li>Nios II embedded<br/>processor support</li> <li>DSP blocks</li> <li>Large on-chip memory</li> <li>High-speed I/O &amp;<br/>memory interfaces</li> <li>Broad IP portfolio<br/>support</li> </ul>                                                                                                            |

|                | Stratix                 | Stratix <sup>®</sup> architecture with high-<br>speed signaling support                                                                                               | <ul> <li>All Stratix features</li> <li>3.125-Gbps transceivers</li> <li>1-Gbps DPA</li> <li>Receiver equalization &amp; transmitter pre-emphasis</li> <li>Broad IP portfolio</li> </ul>                                                                                                                             |

|                  |                                                        |                                                                                                                                                                                                     | support                                                                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                        |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                  |

| Structured ASICs | HARDCOPY"II                                            | <ul> <li>Low-cost structured ASIC solution with:</li> <li>Fine-grained structured cell architecture</li> <li>Prototype with Stratix II FPGA</li> <li>Same design flow as Stratix II FPGA</li> </ul> | <ul> <li>All Stratix II features</li> <li>Guaranteed seamless<br/>migration of FPGA-<br/>proven designs</li> <li>Supported by all major<br/>EDA vendors</li> <li>50 percent lower<br/>power than Stratix II<br/>FPGA</li> <li>350-MHz performance</li> <li>Broad IP portfolio<br/>support</li> </ul>                             |

|                  | HARDCOPY <sup>™</sup><br>HardCopy Stratix <sup>™</sup> | Low-cost structured ASIC solution<br>with:<br>Up to 1 million gates<br>Prototype with Stratix<br>FPGA<br>Same design flow as<br>Stratix FPGA                                                        | <ul> <li>All Stratix features</li> <li>Guaranteed seamless<br/>migration of FPGA-<br/>proven designs</li> <li>Supported by all major<br/>EDA vendors</li> <li>~40 percent lower<br/>power than Stratix FPGA</li> <li>~50 percent higher<br/>performance than Stratix<br/>FPGA</li> <li>Broad IP portfolio<br/>support</li> </ul> |

### **MAX II Device Family Overview**

The MAX<sup>®</sup> II device family is a non-volatile, instant-on programmable logic family with a groundbreaking new CPLD architecture. The new architecture delivers half the cost, one-tenth the power, four times the density, and twice the performance of previous MAX devices. The foundation of these superior results is an architecture that provides all of the advantages of the MAX brand of CPLDs, while leveraging Altera's expertise in look-up table (LUT)-based architectures. The LUT-based architecture delivers the maximum logic capability in the smallest I/O pad-constrained space. As a result, MAX II CPLDs deliver the lowest cost, lowest power, and highest density of any CPLD family.

Based on a cost-optimized 0.18-µm six-layer metal flash process, the MAX II device family has all of the benefits of CPLDs, such as non-volatility, instant-on, ease-of-use, and fast propagation delays. Targeted for general-purpose, low-density logic applications, MAX II devices are ideal for interface bridging, I/O expansion, device configuration, and power-up sequencing. In addition to these traditional CPLD applications, MAX II devices target an extensive number of low-density programmable logic applications previously implemented in FPGAs, ASSPs, and standard logic devices.

MAX II devices offer densities ranging from 240 to 2,210 logic elements (LEs) and up to 272 user I/O pins. Table 1 outlines the MAX II device family members and features. Table 2 shows an overview of MAX II device packaging and I/O pin counts.

| Table 1. MAX II Device Overview                          |          |          |           |           |

|----------------------------------------------------------|----------|----------|-----------|-----------|

| Feature                                                  | EPM240/G | EPM570/G | EPM1270/G | EPM2210/G |

| LEs                                                      | 240      | 570      | 1,270     | 2,210     |

| Typical Equivalent Macrocells                            | 192      | 440      | 980       | 1,700     |

| Maximum User I/O Pins                                    | 80       | 160      | 212       | 272       |

| User Flash Memory Bits                                   | 8,192    | 8,192    | 8,192     | 8,192     |

| $t_{\mbox{\tiny PD1}}$ Corner-to-Corner Performance (ns) | 4.7      | 5.5      | 6.3       | 7.1       |

| t <sub>PD2</sub> Fastest Performance (ns)                | 3.8      | 3.7      | 3.7       | 3.7       |

| Device Availability                                      | Now      | Now      | Now       | Now       |

| Table 2. MAX II Device Package & Maximum User I/O Pins ( <u>1)</u> |          |          |           |           |  |  |

|--------------------------------------------------------------------|----------|----------|-----------|-----------|--|--|

| Package (Size)                                                     | EPM240/G | EPM570/G | EPM1270/G | EPM2210/G |  |  |

| 100-Pin Thin-Quad Flat Pack (TQFP)<br>(16 mm x 16 mm)              | 80       | 76       |           |           |  |  |

| 144-Pin TQFP<br>(22 mm x 22 mm)                                    |          | 116      | 116       |           |  |  |

| 256-Pin FineLine BGA <sup>®</sup> <u>(2)</u><br>(17 mm x 17 mm)    |          | 160      | 212       | 204       |  |  |

| 324-Pin FineLine BGA<br>(19 mm x 19 mm)                            |          |          |           | 272       |  |  |

### **Stratix II Device Family Overview**

Altera introduces Stratix<sup>®</sup> II devices, the industry's biggest and fastest FPGAs. Based on the award-winning Stratix device family, Stratix II FPGAs feature a new and innovative logic structure that allows designers to conserve device resources by packing more functionality into less area, dramatically reducing device costs. Built on a 90-nm process technology, the new logic structure delivers on average 50 percent faster core performance and more than twice the logic capacity, and costs 40 percent less than first-generation Stratix devices. Support for internal clock frequency rates of up to 500 MHz and typical design performance at over 250 MHz mean that designers can now get fast system performance with the time-saving advantages inherent in programmable logic solutions.

Based on a 1.2-V, 90-nm, SRAM process, Stratix II devices are available in densities ranging from 15,600 to 179,400 equivalent logic elements (LEs) and up to 9 Mbits of on-chip RAM. Stratix II devices offer up to 384 (18 x18) embedded multipliers in highly optimized digital signal processing (DSP) blocks and source-synchronous differential signaling with dedicated dynamic phase alignment (DPA) circuitry operating at up to 1 Gbps. Stratix II devices also have dedicated serializer/deserializer (SERDES) circuitry to support the LVDS and HyperTransport™ differential I/O electrical standards, and support high-speed communication interfaces—including the 10 Gigabit Ethernet XSBI, SFI-4, SPI-4.2, HyperTransport, RapidIO<sup>™</sup>, and UTOPIA IV standards. With up to 12 phase-locked loops (PLLs) and 16 global clock networks, the Stratix II FPGA family offers a complete clock management solution including a hierarchical clock structure. In addition, Stratix II devices offer design security, on-chip termination, and remote system upgrade capabilities.

System designers requiring a low-risk cost-reduction path for high-volume production can easily migrate their Stratix II FPGA designs to structured-ASIC production with <u>HardCopy<sup>®</sup> II devices</u>. HardCopy II devices significantly minimize

migration risk because they are generated directly from a Stratix II FPGA and preserve the Stratix II architecture's high density, high performance, industry-leading functionality, and enhanced timing features. This seamless migration process guarantees first-time success for high-volume production, rewarding system designers with minimum time-tomarket at the lowest cost.

Table 1 outlines the Stratix II device family members and features. Table 2 shows an overview of Stratix II device packaging and I/O pin counts.

| Table 1. Stratix II Device Overview |         |           |           |           |           |           |  |  |

|-------------------------------------|---------|-----------|-----------|-----------|-----------|-----------|--|--|

| Feature                             | Device  |           |           |           |           |           |  |  |

|                                     | EP2S15  | EP2S30    | EP2S60    | EP2S90    | EP2S130   | EP2S180   |  |  |

| Adaptive Logic Modules (ALMs) (1)   | 6,240   | 13,552    | 24,176    | 36,384    | 53,016    | 71,760    |  |  |

| Equivalent Logic Elements (LEs) (1) | 15,600  | 33,880    | 60,440    | 90,960    | 132,540   | 179,400   |  |  |

| M512 RAM Blocks (512 Bits + Parity) | 104     | 202       | 329       | 488       | 699       | 930       |  |  |

| M4K RAM Blocks (4 Kbits + Parity)   | 78      | 144       | 255       | 408       | 609       | 768       |  |  |

| M-RAM Blocks (512 Kbits + Parity)   | 0       | 1         | 2         | 4         | 6         | 9         |  |  |

| Total RAM bits                      | 419,328 | 1,369,728 | 2,544,192 | 4,520,448 | 6,747,840 | 9,383,040 |  |  |

| DSP Blocks                          | 12      | 16        | 36        | 48        | 63        | 96        |  |  |

| Embedded Multipliers (2)            | 48      | 64        | 144       | 192       | 252       | 384       |  |  |

| PLLs <u>(3)</u>                     | 6       | 6         | 12        | 12        | 12        | 12        |  |  |

| Maximum User I/O Pins               | 366     | 500       | 718       | 902       | 1,126     | 1,170     |  |  |

| Availability                        | Now     | Now       | Now       | Now       | Now       | Now       |  |  |

Notes to Table 1:

1. Each ALM is equivalent to 2.5 logic elements (LEs).

2. Each DSP block in Stratix II devices can implement four 18×18 multipliers or one 36×36 multiplier. To obtain the total number of 36×36 multipliers per device, divide the total number of 18×18 multipliers by a factor of 4.

3. Includes both fast and enhanced PLLs.

| Table 2. Stratix II Device Package & Maximum User I/O Pins    |        |        |        |                |                |         |  |

|---------------------------------------------------------------|--------|--------|--------|----------------|----------------|---------|--|

| Package Size                                                  | Device |        |        |                |                |         |  |

| (mm x mm)                                                     | EP2S15 | EP2S30 | EP2S60 | EP2S90         | EP2S130        | EP2S180 |  |

| 484-Pin FineLine BGA <sup>®</sup> (FBGA) Package<br>(23 x 23) | 342    | 342    | 334    |                |                |         |  |

| 484-Pin Hybrid FBGA<br>(27 x 27)                              |        |        |        | 308 <u>(1)</u> |                |         |  |

| 672-Pin FBGA<br>(27 x 27)                                     | 366    | 500    | 492    |                |                |         |  |

| 780-Pin FBGA<br>(29 x 29)                                     |        |        |        | 534 <u>(1)</u> | 534 <u>(1)</u> |         |  |

| 1,020-Pin FBGA<br>(33 x 33)                                   |        |        | 718    | 758            | 742            | 742     |  |

| 1,508-Pin FBGA<br>(40 x 40)                                   |        |        |        | 902            | 1,126          | 1,170   |  |

## **Cyclone II FPGA Family Overview**

Altera<sup>®</sup> Cyclone<sup>™</sup> II devices are designed on an all-layer-copper, low-k, 1.2-V SRAM process and are optimized for the smallest possible die size. Built on TSMC's highly successful 90-nm process technology using 300-mm wafers, Cyclone II devices offer higher densities, more features, exceptional performance, and the benefits of programmable logic at ASIC prices. Cyclone II devices offer from 4,608 to 68,416 logic elements (LEs) and are designed with an optimal set of features, including embedded 18 x 18 multipliers, dedicated external memory interface circuitry, 4-kbit embedded memory blocks, phase-locked loops (PLLs), and high-speed differential I/O capabilities.

Cyclone II devices extend the reach of FPGAs further into cost-sensitive, high-volume applications, continuing the success of the first-generation Cyclone device family. Table 1 outlines the Cyclone II FPGA family's features and availability.

| Table 1. Cyclone II FPGA Overview             |         |         |         |         |         |           |

|-----------------------------------------------|---------|---------|---------|---------|---------|-----------|

| Device                                        | EP2C5   | EP2C8   | EP2C20  | EP2C35  | EP2C50  | EP2C70    |

| LEs                                           | 4,608   | 8,256   | 18,752  | 33,216  | 50,528  | 68,416    |

| M4K RAM Blocks<br>(4 kbits + 512 Parity Bits) | 26      | 36      | 52      | 105     | 129     | 250       |

| Total RAM Bits                                | 119,808 | 165,888 | 239,616 | 483,840 | 594,432 | 1,152,000 |

| Embedded<br>18 x 18 Multipliers               | 13      | 18      | 26      | 35      | 86      | 150       |

| PLLs                                          | 2       | 2       | 4       | 4       | 4       | 4         |

| Maximum User I/O Pins                         | 142     | 182     | 315     | 475     | 450     | 622       |

| Differential Channels                         | 58      | 77      | 132     | 205     | 193     | 262       |

| Availability (1)                              | Q3 2005 | Q3 2005 | Q2 2005 | Now     | Q3 2005 | Q2 2005   |

#### Note to Table 1:

1. More information on the lead times for these devices is available from local Altera sales representatives.

Table 2 shows an overview of Cyclone II device packaging and user I/O pin counts.

| Table 2. Cyclone II Device Packages & Maximum User I/O Pins |            |       |            |        |        |        |

|-------------------------------------------------------------|------------|-------|------------|--------|--------|--------|

| Package Size<br>(mm x mm)                                   | EP2C5      | EP2C8 | EP2C20     | EP2C35 | EP2C50 | EP2C70 |

| 144-Pin TQFP <u>(1)</u><br>(22 x 22)                        | 89         | 85    |            |        |        |        |

| 208-Pin PQFP <u>(2)</u><br>(30.35 x 30.35)                  | 142        | 138   | <u>(4)</u> |        |        |        |

| 256-Pin FineLine BGA <u>(3)</u><br>(17 x 17)                | <u>(4)</u> | 182   | 152        |        |        |        |

| 484-Pin FineLine BGA<br>(23 x 23)                           |            |       | 315        | 322    | 294    |        |

| 672-Pin FineLine BGA<br>(27 x 27)                           |            |       |            | 475    | 450    | 422    |

| 896-Pin FineLine BGA<br>(31 x 31)                           |            |       |            |        |        | 622    |

#### Notes to Table 2:

- 1. TQFP = Thin quad flat pack

- 2. PQFP = Plastic quad flat pack

- 3. BGA = Ball-grid array

- 4. These devices will be supported in a future version of the Quartus<sup>®</sup> II software. Contact Your local Altera sales representative for more information.

Table 3 shows the appropriate configuration devices to use for Cyclone II devices.

| Table 3. Appropriate Configuration Devices for Cyclone II FPGAs |       |                              |        |        |        |        |  |  |

|-----------------------------------------------------------------|-------|------------------------------|--------|--------|--------|--------|--|--|

| Configuration Device                                            | _     | Cyclone II Devices Supported |        |        |        |        |  |  |

| Configuration Device                                            | EP2C5 | EP2C8                        | EP2C20 | EP2C35 | EP2C50 | EP2C70 |  |  |

| EPCS1                                                           | Х     |                              |        |        |        |        |  |  |

| EPCS4                                                           | Х     | X                            | X      |        |        |        |  |  |

| EPCS16                                                          | Х     | X                            | X      | X      | Х      | X      |  |  |

| EPCS64                                                          | Х     | Х                            | X      | X      | Х      | X      |  |  |

### MAX 3000A CPLD Family Overview

Altera's MAX<sup>®</sup> 3000A CPLD family is manufactured on a cost-optimized 0.30-µm, four-layer-metal process, and ranges in density from 32 to 512 macrocells. Available in both commercial and industrial grades in popular speed grades and packages, the 3.3-V MAX 3000A CPLD family is ideal for cost-sensitive, high-volume applications.

Table 1 lists the MAX 3000A device offerings.

### Table 1. MAX 3000A Device Overview (3.3 V)

|                                   | Device   |          |          |          |          |  |  |  |

|-----------------------------------|----------|----------|----------|----------|----------|--|--|--|

| Feature                           | EPM3032A | EPM3064A | EPM3128A | EPM3256A | EPM3512A |  |  |  |

| Usable Gates                      | 600      | 1,250    | 2,500    | 5,000    | 10,000   |  |  |  |

| Macrocells                        | 32       | 64       | 128      | 256      | 512      |  |  |  |

| Maximum User I/O Pins             | 34       | 66       | 96       | 158      | 208      |  |  |  |

| t <sub>PD</sub> (ns) <u>(1)</u>   | 4.5      | 4.5      | 5.0      | 7.5      | 7.5      |  |  |  |

| <b>t</b> ₅u (ns) <u>(2)</u>       | 2.9      | 2.8      | 3.3      | 5.2      | 5.6      |  |  |  |

| t <sub>co1</sub> (ns) <u>(3)</u>  | 3.0      | 3.1      | 3.4      | 4.8      | 4.7      |  |  |  |

| f <sub>слт</sub> (MHz) <u>(4)</u> | 227.3    | 222.2    | 192.3    | 126.6    | 116.3    |  |  |  |

| Package                           |          |          | I/O Pins |          |          |  |  |  |

| 44-Pin PLCC <u>(5)</u>            | 34       | 34       |          |          |          |  |  |  |

| 44-Pin TQFP <u>(6)</u>            | 34       | 34       |          |          |          |  |  |  |

| 100-Pin TQFP                      |          | 66       | 80       |          |          |  |  |  |

| 144-Pin TQFP                      |          |          | 96       | 116      |          |  |  |  |

| 208-Pin PQFP (7)                  |          |          |          | 158      | 172      |  |  |  |

| 256-Pin FineLine BGA® (8)         |          |          | 98       | 161      | 208      |  |  |  |

## Xilinx (<u>www.xilinx.com</u>)

|                                  | Technology Solutions                                                                                        | Entire Site                                                 |

|----------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Home                             | Technology Solutions Products & Services                                                                    | s Market Solutions Sup                                      |

| Programma                        | ble Logic   DSP   Embedded Processing   Connec<br>Xilinx : <u>Technology Solutions</u> : Programmable Logic | tivity   Memory   Power   Signal Inte                       |

| Virtex-4 FPGAs                   | •                                                                                                           | 1                                                           |

| Virtex-II Pro Platform<br>FPGAs  | Programmable Logic                                                                                          | 90<br>F                                                     |

| Virtex-II Platform FPGAs         | The Programmable Logic area provides a complete                                                             |                                                             |

| Virtex Series                    | easy access to all the information you need to desi                                                         |                                                             |

| Spartan-3E FPGAs                 | silicon devices                                                                                             | -                                                           |

| Spartan-3 FPGAs                  | FPGA                                                                                                        |                                                             |

| Spartan-IIE FPGAs                | LLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLL                                                                      |                                                             |

| Spartan-II FPGAs                 | EasyPath FPGAs                                                                                              |                                                             |

| Spartan-XL FPGAs                 | Virtex™ Series                                                                                              |                                                             |

| Spartan FPGAs                    |                                                                                                             |                                                             |

| CoolRunner-II CPLDs              | Virtex-4 FPGAs                                                                                              | Virtex-II Platform FPG                                      |

| CoolRunner XPLA3 CPLDs           | Virtex-II Pro / ProX Platform FPGAs                                                                         | Virtex / E / EM FPGAs                                       |

| XC9500 Series CPLDs              | Spartan™ Series                                                                                             |                                                             |

| CPLD Tutorial                    | Spartan-3E FPGAs                                                                                            | Spartan-II FPGAs                                            |

| Configuration Storage<br>Devices | <ul> <li>Spartan-3 FPGAs</li> <li>Spartan-IIE FPGAs</li> </ul>                                              | <ul> <li>Spartan-XL FPGAs</li> <li>Spartan FPGAs</li> </ul> |

| Aerospace and Defense            |                                                                                                             | - Opartan FF GAS                                            |

| RocketPHY                        | CPLD                                                                                                        |                                                             |

| XA Automotive                    |                                                                                                             |                                                             |

|                                  | CoolRunner™-II CPLDs                                                                                        | CoolRunner XPLA3 C                                          |

### Configuration Storage Devices

Xilinx offers a range of configuration storage devices to configure all Xilinx FPGA

- Platform FLASH

- System ACE

- Legacy PROM

#### Aerospace and Defense

Xilinx has created a new family of devices that are hardened against the effects c

- Overview

- Product Engineering

- Applications

Radiation Effects

Cable Support

Programmer Solutions

- SEE Consortium

- Flight Heritage

### RocketPHY

RocketPHY<sup>™</sup> is a family of 10 Gbps single-chip physical layer transceivers that are optimi interconnect applications and are compliant with industry datacom, telecom and storage a standards including Telcordia, OIF and IEEE 802.3ae.

#### Xilinx Automotive

$\overline{X}$ ilinx has created a new family of devices with an extended industrial temperature called the IQ Solutions.

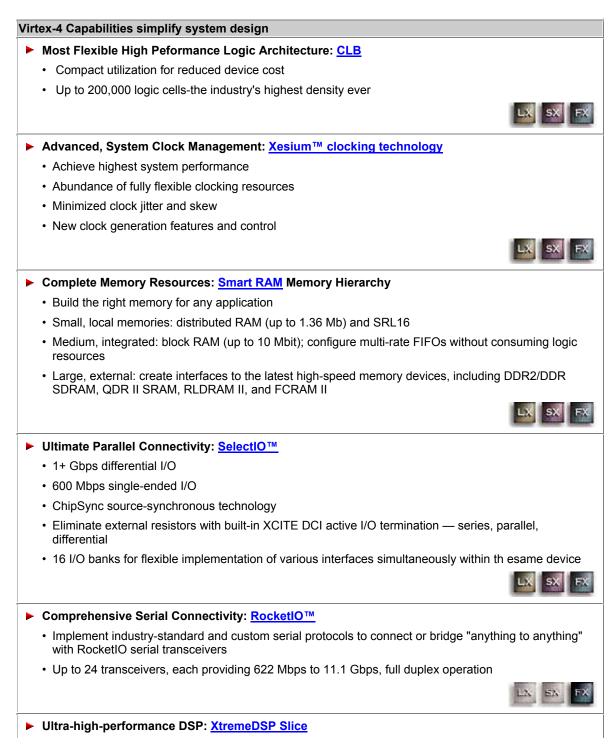

### Virtex-4 FPGA Family Capabilities

Virtex-4<sup>™</sup> family FPGAs offer the functionality and performance to address the widest range of demanding applications. We began with the industry-leading capabilities of Virtex-II Pro devices. Then we added enhancements that accelerate productivity by simplifying system design and providing the margin that makes it easy to achieve design targets.

|               |                                                            | Virtex-4 l    | X (Logic)       |                   |                 |               |               |                   |               | Virtex-4         | SX (Signal       | Processing)          | Virtex-4 F        | X (Embedd        | ed Processi       | ng & Serial        | Connectivity    | 0          |

|---------------|------------------------------------------------------------|---------------|-----------------|-------------------|-----------------|---------------|---------------|-------------------|---------------|------------------|------------------|----------------------|-------------------|------------------|-------------------|--------------------|-----------------|------------|

|               |                                                            | XC4VLX15      | XC4VLX25        | XC4VLX40          | XC4VLX60        | XC4VLXB0      | XC4VLX100     | XC4VLX160         | XC4VLX200     | XC4V5X25         | XC4V5X35         | XC4V5X55             | XC4VFX12          | XC4VFX20         | XC4 VFX40         | XC4VFX60           | XC4VFX100       | XC4VFX14   |

|               | CLB Array (Row x Column)                                   | 64 x 24       | 96 x 28         | 128 x 36          | 128×52          | 160 x 56      | 192 x 64      | 192 x 88          | 192 x 116     | 64 x 40          | 96 x 40          | 128 x 48             | 64x24             | 64 x 36          | 96 x 52           | 128 x 52           | 160 x 68        | 192 x 84   |

| CLB Resources | Slices                                                     | 6,144         | 10,752          | 18,432            | 26,624          | 35,840        | 49,152        | 67,584            | 89,088        | 10,240           | 15,360           | 24,576               | 5,472             | 8,544            | 18,624            | 25,280             | 42,176          | 63,168     |

| CED Resources | Logic Cells                                                | 13,824        | 24,192          | 41,472            | 59,904          | 80,640        | 110,592       | 152,064           | 200,448       | 23,040           | 34,560           | 55,296               | 12,312            | 19,224           | 41,904            | 56,880             | 94,896          | 142,128    |

|               | CL 8 Rip Rops                                              | 12,288        | 21,504          | 36,864            | 53,248          | 71,680        | 98,304        | 135,168           | 178,176       | 20,480           | 30,720           | 49,152               | 10,944            | 17,068           | 37,248            | 50,560             | 84,352          | 126,336    |

| Memory        | Max. Distributed RAM Bits                                  | 98,304        | 172,032         | 294,912           | 425,984         | 573,440       | 786,432       | 1,081,344         | 1,425,408     | 163,840          | 245,760          | 393,216              | 87,552            | 136,704          | 297,984           | 404,480            | 674,816         | 1,010,688  |

| Resources     | Block RAM/FIFO w/ECC (18 kbits each)                       | 48            | 72              | 96                | 160             | 200           | 240           | 288               | 336           | 128              | 192              | 320                  | 36                | 68               | 144               | 232                | 376             | 552        |

|               | Total Block RAM (Hoits)                                    | 864           | 1,296           | 1,728             | 2,880           | 3,600         | 4,320         | 5,184             | 6,048         | 2,304            | 3,456            | 5,760                | 648               | 1,224            | 2,592             | 4,176              | 6,768           | 9,936      |

| Clock         | Digital Clock Managers (DCM)                               | 4             | 8               | 8                 | 8               | 12            | 12            | 12                | 12            | 4                | 8                | 8                    | 4                 | 4                | 8                 | 12                 | 12              | 20         |

| Resources     | Phase-matched Clock Dividers (PMCD)                        | 0             | 4               | 4                 | 4               | 8             | 8             | 8                 | 8             | 0                | 4                | 4                    | 0                 | 0                | 4                 | 8                  | 8               | 8          |

|               | Max Select 1/0 <sup></sup>                                 | 320           | 448             | 640               | 640             | 768           | 960           | 960               | 960           | 320              | 448              | 640                  | 320               | 320              | 448               | 576                | 768             | 896        |

|               | Total I/O Banks                                            | 9             | 11              | 13                | 13              | 15            | 17            | 17                | 17            | 9                | 11               | 13                   | 9                 | 9                | 11                | 13                 | 15              | 17         |

| I/O Resources | Digitally Controlled Impedence                             | Yes           | Yes             | Yes               | Yes             | Yes           | Yes           | Yes               | Yes           | Yes              | Yes              | Yes                  | Yes               | Yes              | Yes               | Yes                | Yes             | Yes        |

|               | Max Differential VO Pairs                                  | 160           | 224             | 32.0              | 320             | 384           | 480           | 480               | 480           | 160              | 224              | 320                  | 160               | 160              | 224               | 288                | 384             | 448        |

|               | VO Standards                                               | LDT-25, LVDS- | 25, LVDSEXT-25, | BLVD 5-25, ULV DS | -25, LVPECL-25, | IVCMOS25, IVC | MOS18, LVCMOS | 15, PC133, LVITL, | LVCM0533, PCH | X, PC166, GTL, 6 | STL+, HSTLI (1.9 | W, 1.8V), HSTL II (1 | 5V(1.8V), HSTL II | (1.5V,1.8V), HST | L IV (1.5V,1.8V), | SSTL21, SSTL211, S | STL181, SSTL181 |            |

| DSP Resources | XtremeDSP <sup>-</sup> Slices                              | 32            | 48              | 64                | 64              | 80            | 96            | 96                | 96            | 128              | 192              | 512                  | 32                | 32               | 48                | 128                | 160             | 192        |

| Embedded      | PowerPC <sup></sup> Processor Blocks                       | -             | -               | -                 | -               |               |               |                   |               | -                |                  | -                    | 1                 | 10               | 2                 | 2                  | 2               | 2          |

| Hard IP       | 10/100/1000 Ethernet MAC Blocks                            | -             | -               | -                 | -               | -             | -             | -                 | -             | -                | -                | -                    | 2                 | 2                | 4                 | 4                  | 4               | 4          |

| Resources     | Rocket10 <sup>—</sup> Serial Transceivers                  | -             | -               | -                 | -               | -             | -             | -                 | -             | -                | ÷.               | -                    | 0                 | 8                | 12                | 16                 | 20              | 24         |

| Speed         | Commercial (slowest to fastest)                            | -10, -11, -12 | -10, -11, -12   | -10, -11, -12     | -10, -11, -12   | -10, -11, -12 | -10, -11, -12 | -10, -11, -12     | -10, -11      | -10, -11, -12    | -10, -11, -12    | -10, -11, -12        | -10, -11, -12     | -10, -11, -12    | -10, -11, -12     | -10, -11, -12      | -10, -11, -12   | -10, -11   |

| Grades        | Industrial (slowest to fastest)                            | -10, -11      | -10, -11        | -10, -11          | -10, -11        | -10, -11      | -10, -11      | -10, -11          | -10           | -10, -11         | -10, -11         | -10, -11             | -10, -11          | -10, -11         | -10, -11          | -10, -11           | -10, -11        | -10        |

|               | Configuration Memory Bits                                  | 4,765,568     | 7,819,904       | 12,259,712        | 17,717,632      | 23,291,008    | 30,711,680    | 40,347,008        | 51,367,808    | 9,147,648        | 13,700,288       | 22,745,216           | 4,765,568         | 7,242,624        | 13,550,720        | 21,002,880         | 33,065,408      | 47,856,896 |

|               | EasyPath <sup></sup> Cost Reduction Solutions <sup>1</sup> | -             | XCE4VLX25       | XCE4VLX40         | XCE4VLX60       | XCE4VLX80     | XCE4VLX100    | XCE4VLX160        | XCE4VLX200    | XCE4V5X25        | XCE4/5X35        | XCE4V5X55            | -                 | XCE4VEX20        | XCE4VFX40         | XCE4VFX60          | XCE4VFX100      | XCE4VFX140 |

#### Xilinx Virtex-4 Series FPGAs

# Spartan-IIE Product Overview

You are facing tremendous design challenges. Rapidly evolving standards, shifting market requirements, intense competition, and the demands for lower costs make your job more difficult than ever before. How do you create new consumer products on schedule and under budget, without losing your peace of mind?

To be successful in this tough, competitive marketplace, you need a fast, inexpensive, and flexible design solution that you can re-program in the lab and at your customer's site. You need fast, reliable performance, and the lowest cost per I/O pin in the industry - that's what you get with Spartan IIE FPGAs. There is no faster, safer, or lower cost way to develop next-generation consumer products.

## The Lowest Cost Solution for Consumer Applications

Spartan-IIE FPGAs give you everything you need to create cost-optimized, flexible, feature-rich products; and you'll find they're far easier (and less expensive) to develop than any ASIC. With the Spartan-IIE family, you get:

- Densities from 50K to 600K system gates

- Superior I/O capabilities

- Up to 514 I/O more than any other low-cost FPGA

- Supports 19 standards, including LVDS, HSTL, and PCI

- A low cost per I/O of any programmable solution

- A seamless path for density migration

- A robust feature set You get DLLs, distributed RAM, and block RAM, delivering the resources you need to develop today's digital convergence products.

- The <u>MicroBlaze soft processor</u> Reduce your overall design cost and device count with this low cost, easy-to-use soft processor solution (an excellent field programmable controller).

- <u>XtremeDSP</u> You get over one billion MACs/sec/dollar, the most cost-effective programmable DSP solution.

- <u>ISE software tools</u> You'll finish your design faster, and reduce your development costs even further.

- Extensive <u>IP core support</u> We offer a wide range of cores including PCI and DSP algorithms, to increase your productivity and decrease design time.

## Spartan-IIE Family at a Glance

Feature/ Product XC2S50E XC2S100E XC2S150E XC2S200E XC2S300E XC2S400E XC2S600E

| System<br>Gates                 | 50K         | 100K        | 150K        | 200K        | 300K        | 400K        | 600K        |

|---------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Logic<br>Cells                  | 1,728       | 2,700       | 3,888       | 5,292       | 6,912       | 10,800      | 15,552      |

| BRAM<br>(Kbits)                 | 32          | 40          | 48          | 56          | 64          | 160         | 288         |

| Delay<br>Lock<br>Loops<br>(DLL) | 4           | 4           | 4           | 4           | 4           | 4           | 4           |

| Max.<br>Dist.                   | 24          | 37.5        | 54          | 73.5        | 96          | 150         | 216         |

| RAM<br>(Kbits)<br>Max           |             |             |             |             |             |             |             |

| Available<br>User I/O           | 182         | 202         | 265         | 289         | 329         | 410         | 514         |

| Package                         | User<br>I/O |

| PQ208<br>TQ144                  | 146<br>102  | 146<br>102  | 146         | 146         | 146         |             |             |

| FT256                           | 182         | 182         | 182         | 182         | 182         | 182         |             |

| FG456<br>FG676                  |             | 202         | 265         | 289         | 329         | 329<br>410  | 329<br>514  |

# **CoolRunner-II Product Overview**

## Get the benefits of CoolRunner-II RealDigital CPLDs for your next design:

- As low as 28.8µW standby power

- Up to 323MHz performance

- Unparalleled design security

- Highest I/O count per macrocell

## **CoolRunner-II Features and Benefits**

Features

- 32 to 512 macrocell device selection

- 1.8 volt supply voltage with 1.5 to 3.3V I/Os

- · Four levels of design security

- RealDigital CPLD technology

- DataGATE

- Multiple I/O banking

- Input hysteresis and programmable grounds

- Dual edge-triggered flip-flops/ ClockDivide

- Multiple LVCMOS, HSTL, SSTL I/O

- Advanced packaging

- Superior pin locking

Benefits

- Wide range of densities for multiple applications

- Eliminates the need for voltage converters

- Prevents pattern theft

- Advanced low power, high speed programmable logic

- Unique features for power saving

- Supports different voltage levels in the same device

- Improved signal integrity for high speed I/O

- Higher performance and more versatility compared to any competing solution

- Flexible I/O supporting wide range of device interface

- Low cost small form factor micro lead frame packages

- Easy redesign during development and enables field upgradability

## **CoolRunner-II Product Overview**

| Feature/Product | XC2C        | XC2C        | XC2C        | XC2C        | XC2C        | XC2C        |

|-----------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Macrocells      | 32A<br>32   | 64A<br>64   | 128<br>128  | 256<br>256  | 384<br>384  | 512<br>512  |

| Tpd(ns)         | 3.8         | 4.6         | 5.7         | 5.7         | 7.1         | 7.1         |

| fsys (MHz)      | 323         | 263         | 244         | 256         | 217         | 179         |

| I/O Banks       | 2           | 2           | 2           | 2           | 4           | 4           |

| Packages        | User<br>I/O | User<br>I/O | User<br>I/O | User<br>I/O | User<br>I/O | User<br>I/O |

| QF32            | 21          |             |             |             |             |             |

| VQ44            | 33          | 33          |             |             |             |             |

| PC44            | 33          | 33          |             |             |             |             |

| QF48            |             | 37          |             |             |             |             |

| CP56            | 33          | 45          |             |             |             |             |

| VQ100           |             | 64          | 80          | 80          |             |             |

| CP132           |             |             | 100         | 106         |             |             |

| TQ144           |             |             | 100         | 118         | 118         |             |

| PQ208           |             |             |             | 173         | 173         | 173         |

| FT256           |             |             |             | 184         | 212         | 212         |

| FG324           |             |             |             |             | 240         | 270         |

|                 |             |             |             |             |             |             |

### Xilinx Automotive (XA)

The Xilinx Automotive (XA) product family is the industry's leading programmable logic family developed specifically for automotive applications. This family is ideal for a wide range of advanced automotive electronics modules and systems ranging from the latest Driver Assistance Systems and Infotainment systems to Reconfigurable Instrument Clusters and ECU Gateways. These applications benefit from the flexibility, reconfigurability and advanced on-chip resources such as multipliers for high speed DSP provided in devices from

the Xilinx automotive industries leading PLD supplier. XA devices include:

- Extended temperature ranges, both Automotive Industrial and Automotive Q-Grade

- Full PPAP support

- Industry-recognized <u>AEC-Q100</u> device-qualification flow

Xilinx is committed to quality and offers a roadmap to address the worldwide automotive quality standard <u>ISO TS 16949</u>, as well as <u>Pb-free packaging to</u> <u>meet the RoHS directive</u>.

|               | Temperati                                      | ure / Grade                                    |

|---------------|------------------------------------------------|------------------------------------------------|

| Product Group | Automotive I                                   | Automotive Q                                   |

| XA FPGA       | $T_J = -40^{\circ}C \text{ to } +100^{\circ}C$ | $T_J = -40^{\circ}C$ to $+125^{\circ}C$        |

| XA CPLD       | T <sub>A</sub> = -40°C to 85°C                 | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$ |

|                                              |               | Device Famil                            | у                              |                                                                                                                     |

|----------------------------------------------|---------------|-----------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------|

| FPGA                                         | CPLD          | Packages                                | Densities                      | Special Feature                                                                                                     |

| <u>Spartan-3</u>                             |               | VQG100,<br>PQG208,<br>FTG256,<br>FTG465 | 50k - 1000k<br>System<br>Gates | Embedded<br>Multipliers for<br>DSP & Digital<br>Clock<br>Management to<br>solves high<br>speed design<br>challenges |

| <u>Spartan-IIE</u>                           |               | TQ144 &<br>FT256                        | 50k - 300k<br>Systems<br>Gates | Embedded DLLs<br>for clock<br>management,<br>Embedded<br>Memory and 19<br>I/O Standards                             |

|                                              | CoolRunner-II | VQG44 &<br>VQG100                       | 32 - 256<br>Macrocells         | Ultra Low Power<br>& up to 8 single<br>ended I/O<br>standards                                                       |

|                                              | <u>9500XL</u> | VQ44 &<br>TQ144                         | 36 - 144<br>Macrocells         | Lowest cost per<br>macrocell                                                                                        |

| Platform<br>Flash<br>Configuration<br>Memory |               | VO20                                    | 1 - 4 Mb                       | In-system<br>programmable                                                                                           |

## Actel (<u>www.actel.com</u>)

### Flash Devices

- ProASIC3: Flash based, reprogrammable devices 30k to 3 million gates

- ProASIC<sup>PLUS</sup>: Flash based, reprogrammable devices 75k to 1 million gates

- ProASIC: Flash based, reprogrammable devices 100k to 450k gates

### Antifuse Devices

- Axcelerator: High-speed antifuse FPGAs with gate densities of up to 2 million equivalent gates

- <u>SX-A / SX</u>: Antifuse devices 8k to 72k gates

- <u>eX</u>: Antifuse devices 3k to 12k gates

- <u>MX</u>: Antifuse devices 3k to 54k gates

### High Performance, Low Cost FLASH FPGAs the only true ASIC alternative

The ProASIC3/E families of Flash FPGAs offer a breakthrough in price, performance, density, and features for today's most demanding applications. The ProASIC3/E families are based on nonvolatile Flash technology and support between 30k to 3M gates and up to 616 high performance I/Os.

### Product Table

|                                    | A3P030             | A3P060     | A3P125 | A3P250         | A3P400         | A3P600         | A3P1000        | A3PE600 | A3PE1500 |

|------------------------------------|--------------------|------------|--------|----------------|----------------|----------------|----------------|---------|----------|

| System Gates                       | 30 k               | 60 k       | 125 k  | 250 k          | 400 k          | 600 k          | 1 M            | 600 k   | 1.5 M    |

| <b>VersaTiles</b><br>(D-Flip-Flop) | 768                | 1,536      | 3,072  | 6,144          | 9,216          | 13,824         | 24,576         | 13,824  | 38,400   |

| RAM kbits<br>(1,024 bits)          | -                  | 18         | 36     | 36             | 54             | 108            | 144            | 108     | 270      |

| 4,608-Bit Blocks                   | -                  | 4          | 8      | 8              | 12             | 24             | 32             | 24      | 60       |

| FlashROM<br>(FROM) bits            | 1 k                | 1 k        | 1 k    | 1 k            | 1 k            | 1 k            | 1 k            | 1 k     | 1 k      |

| Secure<br>(AES) ISP                | No                 | Yes        | Yes    | Yes            | Yes            | Yes            | Yes            | Yes     | Yes      |

| PLLs                               | -                  | 1          | 1      | 1              | 1              | 1              | 1              | 6       | 6        |

| VersaNet Globals                   | 6                  | 18         | 18     | 18             | 18             | 18             | 18             | 18      | 18       |

| I/O Standards                      | Std. &<br>Hot Swap | Std.+      | Std.+  | Std.+/<br>LVDS | Std.+/<br>LVDS | Std.+/<br>LVDS | Std.+/<br>LVDS | Pro     | Pro      |

| <b>I/O Banks</b><br>(+JTAG)        | 2                  | 2          | 2      | 4              | 4              | 4              | 4              | 8       | 8        |

| Single-Ended I/O /                 | Differenti         | al I/O Pai | rs*    | _              |                | _              |                |         |          |

| QN132                              | 81                 |            |        |                |                |                |                |         |          |

| VQ100                              | 79                 | 71         | 71     | 68/13          |                |                |                |         |          |

| FG144                              |                    | 96         | 97     | 97/24          | 97/24          | 97/24          | 97/24          |         |          |

| TQ144                              |                    | 91         | 100    |                |                |                |                |         |          |

| PQ208                              |                    |            | 133    | 151/34         | 151/33         | 154/35         | 154/35         | 147/65  | 147/65   |

| FG256                              |                    |            |        | 157/38         | 178/38         | 179/45         | 179/45         | 165/79  |          |

| FG484                              |                    |            |        |                | 194/38         | 227/56         | 288/68         | 270/135 | 280/136  |

| FG676                              |                    |            |        |                |                |                |                |         | 439/209  |

| FG896                              |                    |            |        |                |                |                |                |         |          |

### Flash Benefits

| Features:                 | Benefits:                                                                                                                                                                                     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>Low Cost</u>           | The world's lowest cost FPGA solution offering industry-leading unit cost and <u>lo</u> system cost.                                                                                          |

| High Performance          | Enhanced, high-performance architecture up to 350MHz operation and 95% logi utilization.                                                                                                      |

| Single Chip               | Does not require additional configuration nonvolatile memory in order to load th configuration data at every system power-up, which <u>reduces cost</u> and increases and system reliability. |

| Live-At-Power-Up          | Greatly simplifies system design, making the device available to perform critica setup tasks and <u>reduce bill-of-materials costs</u> and PCB area.                                          |

| <u>Secure ISP</u>         | Support of built-in AES decryption engine and industry-leading Flash-based AE: for secure remote field updates over public networks with encrypted bitstream.                                 |

| User Nonvolatile Memory   | 1,024 bits of on-chip, user accessible, nonvolatile FlashROM (FROM) that can t diverse system applications.                                                                                   |

| Low Power                 | Maximizes power savings with very limited power-on current surge and no high-<br>transition period, both of which occur on many FPGAs. Offers low dynamic powe<br>consumption.                |

| <u>Firm Errors Immune</u> | Flash cell configuration element cannot be altered by high-energy neutrons and therefore immune, unlike SRAM based FPGAs.                                                                     |

| <u>Device Security</u>    | Utilizes a 128-bit Flash-based lock and inherent Flash technology features, pro-<br>most impenetrable security for programmable logic designs.                                                |

### SX-A / SX FPGAs: Reducing the Cost of Performance

Actel's SX-A/SX devices can match the speed and performance of an ASIC or be used to generate system wide savings by integrating multiple functions into a low-cost single-chip solution. Providing a combination of high speed and low-power SX-A/SX decreases the premium for performance while providing a solution highly secure from reverse engineering.

#### The low cost of integration:

Today's applications require higher speeds and greater density than ever before. Actel's SX-A/SX FPGA families open the door to next generation designs that could not previously be implemented in programmable logic. The expanded capabilities and performance allow products to get to market faster, cost less and generate more revenue. 1

ī.

÷.

Т

÷.

ī

- 1

#### The industries highest design security:

The interconnections within SX-A FPGAs are extremely small, are densely distributed throughout the device, and do not leave an observable signature that can be electrically probed or visually inspected. With these safeguards, SX-A devices are virtually immune to copying and reverse engineering.

#### SX-A / SX Benefits:

- 12,000 to 108,000 usable system gates

- 3.7ns clock-to-output (pin-to-pin)

- 350MHz internal clock frequency

- 66MHz, 64-bit 3.3V/5.0V PCI performance (supporting Target, Master and Master/Target)

- Hot swappable I/Os (SX-A)

- Excellent for ATM, IP, WDM, DBE and SONET applications

- Able to run at OC3 to OC192 data rates

- 2.5V, 3.3V, and 5.0V mixed voltage support

- 100% resource utilization with 100% pin locking

- Low power consumption (less than 1W @ 200MHz)

- Complete BST/JTAG support

#### A54SX-A / SX Selector Guide

#### SX08/08A SX16/16A SX16P SX32/32A SX72A

| Typical Gates        | 8,000  | 16,000 | 16,000 | 32,000 | 72,000  |

|----------------------|--------|--------|--------|--------|---------|

| System Gates         | 12,000 | 24,000 | 24,000 | 48,000 | 108,000 |

| Dedicated Flip Flops | 256    | 528    | 528    | 1080   | 2012    |

| Maximum I/O          | 130    | 177    | 177    | 249    | 360     |

| Logic Modules        | 768    | 1452   | 1452   | 2880   | 6036    |

### Lattice (<u>www.latticesemi.com</u>)

## Leadership FPGA Devices From Lattice

#### Overview

FPGA (Field Programmable Gate Array) solutions from Lattice bring together innovative FPGA architecture and advanced technology in unique ways to deliver performance and cost goals for a wide variety of applications.

Learn about the Lattice FPGA technology roadmap.

#### **High-Volume FPGAs**

- LatticeECP-DSP (<u>EConomyPlus-DSP</u>) FPGA devices combine the optimized LatticeEC fabric with a highperformance embedded sysDSP block that is tailored for the implementation of common DSP functions. See the LatticeECP FPGA Selector Table below.

- LatticeEC (<u>EC</u>onomy) FPGA devices deliver an optimized blend of features, cost and performance for highvolume, cost sensitive applications. See the LatticeEC FPGA Selector Table below.

#### Non-Volatile Infinitely Reconfigurable FPGAs

- ispXP<sup>™</sup> Technology brings together "Instant-On" and High Security and other attributes of non-volatile technologies with the re-configurability of SRAM in a single device. By providing internal non-volatile cells for storing FPGA configuration, customers simplify their designs; they do not require external Boot Prom and thus save space and cost. A non-volatile array distributed within the FPGA device stores the device configuration. At power-up the configuration is transferred from FLASH memory to configuration SRAM in less than 1mS. By eliminating the external configuration bit stream and by providing a security scheme that prevents program read-back, these devices deliver secure FPGA solutions.

- The LatticeXP<sup>™</sup> (eXpanded Programmability) FPGA family combines the optimized FPGA architecture used in the LatticeEC (EConomy) family with ispXP technology implemented on a low-cost 130nm FLASH process to provide "Instant-On", High Security, Non-Volatile, and Reconfigurable features - in a single lowcost chip. See the LatticeXP FPGA Selector Table below.

## LatticeECP and EC Product Family Selector Guide

| Device     | sysDSP<br>Blocks* | 18 x 18<br>Embedded<br>Multipliers* | LUTs<br>(K) | Distributed<br>RAM (K) | EBR Block<br>SRAM (K) | Number<br>of EBR<br>SRAM<br>Blocks | MAX<br>User<br>I/O | PLLs |

|------------|-------------------|-------------------------------------|-------------|------------------------|-----------------------|------------------------------------|--------------------|------|

| <u>EC1</u> | -                 | -                                   | 1.5         | 6                      | 18                    | 2                                  | 112                | 2    |

| <u>EC3</u> | -                 | -                                   | 3.1         | 12                     | 55                    | 6                                  | 160                | 2    |

| ECP6/EC6   | 4                 | 16                                  | 6.1         | 25                     | 92                    | 10                                 | 224                | 2    |

| ECP10/EC10 | 5                 | 20                                  | 10.2        | 41                     | 277                   | 30                                 | 288                | 4    |

| ECP15/EC15 | 6                 | 24                                  | 15.4        | 61                     | 350                   | 38                                 | 352                | 4    |

| ECP20/EC20 | 7                 | 28                                  | 19.7        | 79                     | 424                   | 46                                 | 400                | 4    |

| ECP33/EC33 | 8                 | 32                                  | 32.8        | 131                    | 535                   | 58                                 | 496                | 4    |

\* ECP Devices only

LatticeXP FPGA Product Family Selector Guide

| Device       | LUTs<br>(K) | Distributed RAM<br>(K) | EBR Block<br>SRAM (K) | Number of EBR<br>SRAM Blocks | Max User<br>I/O PLLs |

|--------------|-------------|------------------------|-----------------------|------------------------------|----------------------|

| LFXP3        |             |                        |                       |                              |                      |

| 3.1          | 12          | 54                     | 6                     | 136                          | 2                    |

| <u>LFXP6</u> |             |                        |                       |                              |                      |

| 5.8          | 23          | 90                     | 10                    | 188                          | 2                    |

| LFXP10       |             |                        |                       |                              |                      |

| 9.7          | 39          | 216                    | 24                    | 244                          | 4                    |

| LFXP15       |             |                        |                       |                              |                      |

| 15.4         | 61          | 288                    | 32                    | 300                          | 4                    |

| LFXP20       |             |                        |                       |                              |                      |

| 19.7         | 79          | 414                    | 46                    | 340                          | 4                    |

### ispXPGA Product Family Selector Guide

|                       | FPGA<br>System | sysHSI    | LUTs |               | Block   | Distributed | Max      |

|-----------------------|----------------|-----------|------|---------------|---------|-------------|----------|

| Family                | Gates (K)      | Channels* | (K)  | Logic FFs (K) | RAM (K) | RAM (K)     | User I/O |

| <u>ispXPGA 125/E</u>  | 139            | 4         | 1.9  | 3.8           | 92      | 30          | 176      |

| <u>ispXPGA 200/E</u>  | 210            | 8         | 2.7  | 5.4           | 111     | 43          | 208      |

| <u>ispXPGA 500/E</u>  | 476            | 12        | 7.1  | 14.1          | 184     | 112         | 336      |

| <u>ispXPGA 1200/E</u> | 1,250          | 20        | 15.4 | 30.8          | 414     | 246         | 496      |

Note: 8 PLLs with global clocks and low-skew clock nets per device. \* "E-Series" does not support sysHSI.

# **Altera Development Kits**

Altera<sup>®</sup> development kits provide a complete, high-quality design environment for engineers. A wide variety of kits help simplify the design process and reduce time-to-market. Development kits include software, reference designs, cables, and programming hardware. Table 1 lists Altera development kits.

| Table 1. Altera Development Kits (1)                            |                        |         |

|-----------------------------------------------------------------|------------------------|---------|

| Product Name                                                    | Device                 | Price   |

| <u>High-Speed Development Kit, Stratix GX</u><br>Edition        | Stratix GX<br>EP1SGX40 | \$7,995 |

| DSP Development Kit, Stratix Professional<br>Edition            | Stratix<br>EP1S80      | \$4,995 |

| PCI High-Speed Development Kit, Stratix<br>Professional Edition | Stratix<br>EP1S60      | \$4,995 |

| Nios II Development Kit, Stratix Professional<br>Edition        | Stratix<br>EP1S40      | \$2,495 |

| DSP Development Kit, Stratix Edition                            | Stratix<br>EP1S25      | \$1,995 |

| DSP Development Kit, Stratix II Edition                         | Stratix II<br>EP2S60   | \$1,995 |

| High-Speed Development Kit, Stratix II<br>Edition               | Stratix II<br>EP2S60   | \$1,995 |

| PCI Development Kit, Stratix Edition                            | Stratix<br>EP1S25      | \$1,995 |

| DSP Development Kit, Cyclone II Edition                         | Cyclone II<br>EP2C35   | \$995   |

| Nios II Development Kit, Cyclone<br>Edition <sup>Updated</sup>  | Cyclone<br>EP1C20      | \$995   |

| Nios II Development Kit, Cyclone II<br>Edition                  | Cyclone II<br>EP2C35   | \$995   |

| Nios II Development Kit, Stratix<br>Edition                     | Stratix<br>EP1S10      | \$995   |

| Nios II Development Kit, Stratix II<br>Edition                  | Stratix II<br>EP2S30   | \$995   |

| PCI Development Kit, Cyclone II Edition                         | EP2C35                 | \$995   |

| Nios II Evaluation Kit                                          | Cyclone<br>EP1C12      | \$295   |

| MAX II Development Kit                                          | MAX II<br>EPM1270      | \$150   |

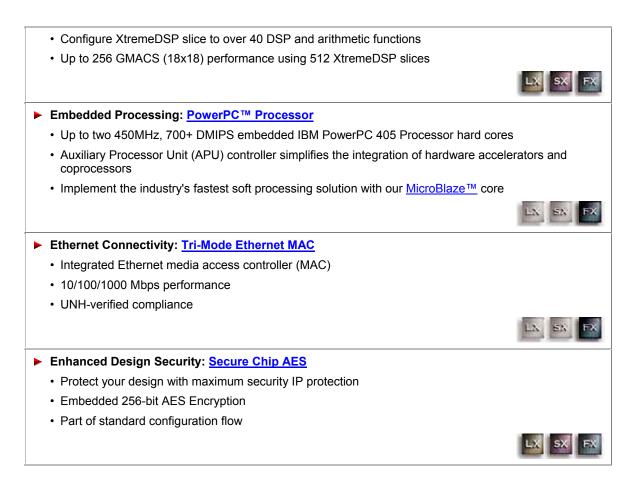

# **University Program Education Kits**

The Altera<sup>®</sup> University Program offers participating universities a UP3 Education Kit with the complete Quartus<sup>®</sup> II design software. This kit (shown in Table 1) provides a comprehensive solution to the programmable logic design challenge.

| Table 1. University Program Education Kits |                                                                                                                                                                                    |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | UP3 Education Kit                                                                                                                                                                  |

| •<br>•<br>•                                | Quartus II development software, version 4.1<br>UP3 development board with a Cyclone™ EP1C6Q240C8 device<br>ByteBlaster™ II download cable<br>Power supply<br>Kit price: \$249 USD |

|                                            | UP2 Education Kit                                                                                                                                                                  |

| •                                          | Quartus II development software, version 4.0<br>UP2 development board with a FLEX 10K <sup>®</sup> EPF10K70 device                                                                 |

Note: Altera strongly recommends using the UP3 education kit over the UP2 kit due to the versatile rich features embedded in it. The UP3 kit comes with the industry's most advanced logic development software tool along with other leading edge products.

### UP3 board - www.slscorp.com

### Similar to UP3 hardware

#### Embedded System Development Kit

The Embedded System Development Kit provides a powerful, low-cost solution for prototyping and rapid development of the products. The ESDK in conjunction with 8051 IDE is an excellent means for system designing, prototyping, emulation and simulation.

The ESDK board comes with a powerful Altera Cyclone FPGA. It gives scope to a hardware design engineer to design, prototype and test IP cores or any hardware design using HDLs like Verilog or VHDL. Using 8051 IDE, one can simulate and test "C" or assembly code. The entire environment helps to quickly implement any processor as well as any real time operating system on the ESDK. The IP for an 8051 micro controller is prebuilt and may be loaded into the FPGA. Using the 8051 IDE, programs may be downloaded and executed on the system. The ESDK board has industry standard interconnections, memory subsystem, multiple clocks for system design, JTAG configuration and expansion headers for greater flexibility and additional user interfaces.

The 8051 board can be used for DSP applications by interfacing directly to a DSP processor or implementing DSP functions inside the FPGA. In short, it is a dual-purpose kit, which can be used for prototyping and developing VLSI designs as well as designing and developing microprocessor based embedded systems.

The ESDK is shipped with Altera Quartus II software starter CD and download cable. Henceforth, cost of buying expensive FPGA design software is saved.

#### Fetures

- Powerful Development Board for FPGA designs

- o Provides an Altera EP1C6Q240 Device and EPCS1 Configuration device

- Supports intellectual property based (IP-based) design both with and without a microprocessor.

- Industry standard interconnection

- USB 2.0 compliant (full & low speed)

- o Two RS 232 Ports

- Parallel Port (IEEE1284)

- PS/2 Port

- Memory Sub System

- o 1Mbyte of SRAM

- 2Mbytes of FLASH

- 2Kbytes of I2C PROM (expandable)

- Multiple Clocks for system design

- JTAG Configuration and debugging

- Expansion headers for greater flexibility and capacity

- 5V Santa Cruz long Expansion Card Header provides 72 I/O for the development of additional boards providing various functionality

- Additional user interface features

- One user-definable 4-bit switch block

- Four user-definable push button switches and one global reset switch

- Four user-definable LEDs

- One 16x2 character display LCD Module

- o I2C Real Time Clock

- 8051 IDE

### Applications

ESDK board is a general-purpose board with lot many peripheral supports.

- With FPGA on the board, the user can develop/test any program written in Hardware Description Language.

- All the peripherals on the board are connected to the I/O lines of the FPGA, so the user can download and test any application related to the available peripherals on the board.

- The ESDK board provides one parallel port and two serial ports to develop/test the applications.

- Applications based on USB, PS2, and I2C etc can be developed/tested.

- The ESDK board is having a 16X2 character LCD which serves as a display device.

- 1Mbyte of SRAM, 2Mbytes of FLASH and 2Kbytes of I2C PROM are provided to develop/test memory related applications.

- ESDK board is shipped with the pre-built 8051 IP core to develop micro controller related applications.

- 8051 IDE includes Cross Compiler, Assembler, Simulator and Emulator.

- **Cross Compiler and Assembler:** Supports Assembly, C and mixed language ('C' + Assembly) programming and creates ROMable code / Intel HEX format file

- Simulator:SLS 8051 IDE Simulator provides all the necessary features to simulate user code.

- Emulator:SLS 8051 IDE Emulator provides all the necessary features for emulation. Some of them are listed below:

- Read and modify internal registers (registers and SFRs)

- Read and modify external RAM locations

- Run from a memory location

- Load an Intel Hex file from the host computer in RAM

- Single-step execution of a program

- Call a user program as a subroutine

- Dump memory data to a terminal

- Set upto 4 breakpoints

## **DSP** Development Kit, Stratix II Edition

The DSP Development Kit, Stratix<sup>®</sup> II Edition delivers a complete digital signal processing (DSP) development environment for design engineers. The kit facilitates the entire design process from design conception through hardware implementation. The DSP Development Kit, Stratix II Edition includes the Stratix II DSP development board, DSP Builder development tool, Quartus<sup>®</sup> II development software, MATLAB/Simulink evaluation software, evaluation intellectual property (IP) cores, system reference designs and labs, as well as power supplies, cables, and documentation.

- Ordering Information

- Development Kit Contents

- Available Documentation

## **Development Kit Contents**

The DSP Development Kit, Stratix II Edition features: